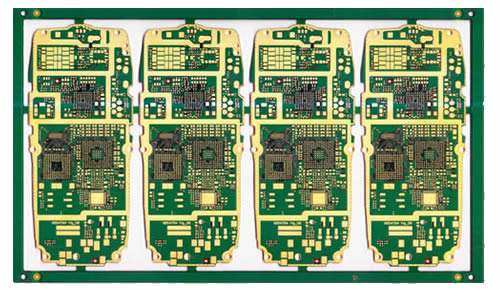

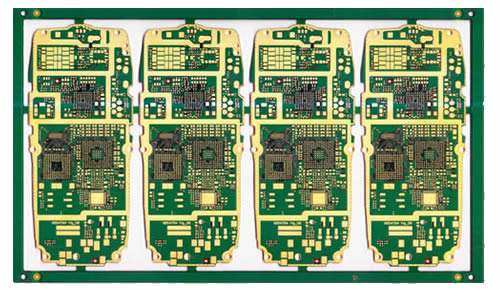

高速信號板PCB設計

在PCB設計中,高速信號板的布局布線和質量分析無疑是工程師們討論的焦點。尤其是如今的電路板工作頻率越來越高,例如一般的數字信號處理(DSP)電路板應用頻率在150-200MHz是很常見的,CPU板在實際應用中達到500MHz以上已經不足為奇,在通信行業中Ghz電路的設計已經十分普及。所有這些PCB板的設計,往往是采用多層板技術來實現。在多層板設計中不可避免地為采用電源層的設計技術。而在電源層設計中,往往由于多種類的電源混合應用而使得PCB設計變為十分復雜。

那么縈繞在PCB工程師中的難題有哪些? PCB的層數如何定義?包括采用多少層?各個層的內容如何安排最合理?如應該有幾層地,信號層和地層如何交替排列等等。

如何設計多種類的電源分塊系統?如3.3V, 2.5V, 5V, 12V 等等。電源層的合理分割和共地問題是PCB是否穩定的一個十分重要的因素。

如何設計去耦電容?利用去耦電容來消除開關噪聲是常用的手段,但如何確定其電容量?電容放置在什么位置?什么時候采用什么類型的電容等等。

如何消除地彈噪聲?地彈噪聲是如何影響和干擾有用信號的?回路(Return Path)噪聲如何消除?很多情況下,回路設計不合理是電路不工作的關鍵,而回路設計往往是工程師最覺得束手無策的工作。

如何合理設計電流的分配?尤其是地電層中電流的分配設計十分困難,而總電流在PCB板中的分配如果不均勻,會直接明顯地影響PCB板的不穩定工作。

另外還有一些常見的如上沖,下沖,振鈴(振蕩),時延,阻抗匹配,毛刺等等有關信號的奇變問題,但這些問題和上述問題是不可分割的。它們之間是因果關系。

總的來說,設計好一個高質量的高速信號板,應該從信號完整性(SI---Signal Integrity)和電源完整性(PI---Power Integrity )兩個方面來考慮。盡管比較直接的結果是從信號完整性上表現出來的,但究其成因,我們絕不能忽略了電源完整性的PCB設計。因為電源完整性直接影響最終高速信號板的信號完整性。

有一個十分大的誤區存在于PCB工程師中間,尤其是那些曾經使用傳統EDA工具來進行高速PCB設計的工程師。有很多工程師曾經問過我們:“為什么用EDA具的SI信號完整性工具分析出來的結果和我們用儀器實際測試的結果不一致,而且往往是分析的結果比較理想?”其實這個問題很簡單。 引起這個問題的原因是:一方面是EDA廠商的技術人員沒有解釋清楚;另一方面是PCB設計人員的對仿真結果的理解問題。我們知道,目前中國市場上使用比較多的EDA工具主要是SI(信號完整性)分析工具,SI 是在不考慮電源的影響下基于布線和器件模型而進行的分析,而且大多數連模擬器件也不考慮(假定是理想的),可想而知,這樣的分析結果和實際結果肯定是有誤差的。因為大多數情況下, PCB板中電源完整性的影響比SI更加嚴重。

那么縈繞在PCB工程師中的難題有哪些? PCB的層數如何定義?包括采用多少層?各個層的內容如何安排最合理?如應該有幾層地,信號層和地層如何交替排列等等。

如何設計多種類的電源分塊系統?如3.3V, 2.5V, 5V, 12V 等等。電源層的合理分割和共地問題是PCB是否穩定的一個十分重要的因素。

如何設計去耦電容?利用去耦電容來消除開關噪聲是常用的手段,但如何確定其電容量?電容放置在什么位置?什么時候采用什么類型的電容等等。

如何消除地彈噪聲?地彈噪聲是如何影響和干擾有用信號的?回路(Return Path)噪聲如何消除?很多情況下,回路設計不合理是電路不工作的關鍵,而回路設計往往是工程師最覺得束手無策的工作。

如何合理設計電流的分配?尤其是地電層中電流的分配設計十分困難,而總電流在PCB板中的分配如果不均勻,會直接明顯地影響PCB板的不穩定工作。

另外還有一些常見的如上沖,下沖,振鈴(振蕩),時延,阻抗匹配,毛刺等等有關信號的奇變問題,但這些問題和上述問題是不可分割的。它們之間是因果關系。

總的來說,設計好一個高質量的高速信號板,應該從信號完整性(SI---Signal Integrity)和電源完整性(PI---Power Integrity )兩個方面來考慮。盡管比較直接的結果是從信號完整性上表現出來的,但究其成因,我們絕不能忽略了電源完整性的PCB設計。因為電源完整性直接影響最終高速信號板的信號完整性。

有一個十分大的誤區存在于PCB工程師中間,尤其是那些曾經使用傳統EDA工具來進行高速PCB設計的工程師。有很多工程師曾經問過我們:“為什么用EDA具的SI信號完整性工具分析出來的結果和我們用儀器實際測試的結果不一致,而且往往是分析的結果比較理想?”其實這個問題很簡單。 引起這個問題的原因是:一方面是EDA廠商的技術人員沒有解釋清楚;另一方面是PCB設計人員的對仿真結果的理解問題。我們知道,目前中國市場上使用比較多的EDA工具主要是SI(信號完整性)分析工具,SI 是在不考慮電源的影響下基于布線和器件模型而進行的分析,而且大多數連模擬器件也不考慮(假定是理想的),可想而知,這樣的分析結果和實際結果肯定是有誤差的。因為大多數情況下, PCB板中電源完整性的影響比SI更加嚴重。

上一新聞:PCB設計檢驗流程

下一新聞:無線充電PCB設計的改進研發